# 4.1 IMM8 CONTROL BYTE OPERATION FOR PCMPESTRI / PCMPESTRM / PCMPISTRI / PCMPISTRM

The notations introduced in this section are referenced in the reference pages of PCMPESTRI, PCMPESTRM, PCMP-ISTRI, PCMPISTRM. The operation of the immediate control byte is common to these four string text processing instructions of SSE4.2. This section describes the common operations.

# 4.1.1 General Description

The operation of PCMPESTRI, PCMPESTRM, PCMPISTRI, PCMPISTRM is defined by the combination of the respective opcode and the interpretation of an immediate control byte that is part of the instruction encoding.

The opcode controls the relationship of input bytes/words to each other (determines whether the inputs terminated strings or whether lengths are expressed explicitly) as well as the desired output (index or mask).

The Imm8 Control Byte for PCMPESTRM/PCMPESTRI/PCMPISTRM/PCMPISTRI encodes a significant amount of programmable control over the functionality of those instructions. Some functionality is unique to each instruction while some is common across some or all of the four instructions. This section describes functionality which is common across the four instructions.

The arithmetic flags (ZF, CF, SF, OF, AF, PF) are set as a result of these instructions. However, the meanings of the flags have been overloaded from their typical meanings in order to provide additional information regarding the relationships of the two inputs.

PCMPxSTRx instructions perform arithmetic comparisons between all possible pairs of bytes or words, one from each packed input source operand. The boolean results of those comparisons are then aggregated in order to produce meaningful results. The Imm8 Control Byte is used to affect the interpretation of individual input elements as well as control the arithmetic comparisons used and the specific aggregation scheme.

Specifically, the Imm8 Control Byte consists of bit fields that control the following attributes:

- Source data format Byte/word data element granularity, signed or unsigned elements

- **Aggregation operation** Encodes the mode of per-element comparison operation and the aggregation of per-element comparisons into an intermediate result

- **Polarity** Specifies intermediate processing to be performed on the intermediate result

- **Output selection** Specifies final operation to produce the output (depending on index or mask) from the intermediate result

# 4.1.2 Source Data Format

| lmm8[1:0]                                                                      | Meaning        | Description                                                 |  |

|--------------------------------------------------------------------------------|----------------|-------------------------------------------------------------|--|

| 00b Unsigned bytes Both 128-bit sources are treated as packed, unsigned bytes. |                |                                                             |  |

| 01b                                                                            | Unsigned words | Both 128-bit sources are treated as packed, unsigned words. |  |

| 10b                                                                            | Signed bytes   | Both 128-bit sources are treated as packed, signed bytes.   |  |

| 11b                                                                            | Signed words   | Both 128-bit sources are treated as packed, signed words.   |  |

#### Table 4-1. Source Data Format

If the Imm8 Control Byte has bit[0] cleared, each source contains 16 packed bytes. If the bit is set each source

contains 8 packed words. If the Imm8 Control Byte has bit[1] cleared, each input contains unsigned data. If the bit is set each source contains signed data.

# 4.1.3 Aggregation Operation

#### Table 4-2. Aggregation Operation

| Imm8[3:2] | Mode          | Comparison                                                                                                              |  |

|-----------|---------------|-------------------------------------------------------------------------------------------------------------------------|--|

| 00b       | Equal any     | The arithmetic comparison is "equal."                                                                                   |  |

| 01b       | Ranges        | Arithmetic comparison is "greater than or equal" between even indexed bytes/words of reg and each byte/word of reg/mem. |  |

|           |               | Arithmetic comparison is "less than or equal" between odd indexed bytes/words of reg and each byte/word of reg/mem.     |  |

|           |               | (reg/mem[m] >= reg[n] for n = even, reg/mem[m] <= reg[n] for n = odd)                                                   |  |

| 10b       | Equal each    | The arithmetic comparison is "equal."                                                                                   |  |

| 11b       | Equal ordered | The arithmetic comparison is "equal."                                                                                   |  |

All 256 (64) possible comparisons are always performed. The individual Boolean results of those comparisons are referred by "BoolRes[*Reg/Mem element index, Reg element index*]." Comparisons evaluating to "True" are represented with a 1, False with a 0 (positive logic). The initial results are then aggregated into a 16-bit (8-bit) intermediate result (IntRes1) using one of the modes described in the table below, as determined by Imm8 Control Byte bit[3:2].

See Section 4.1.6 for a description of the overrideIfDataInvalid() function used in Table 4-3.

| Mode                          | Pseudocode                                                                                        |

|-------------------------------|---------------------------------------------------------------------------------------------------|

| Equal any                     | UpperBound = imm8[0] ? 7 : 15;                                                                    |

| (find characters from a set)  | IntRes1 = 0;                                                                                      |

|                               | For j = 0 to UpperBound, j++                                                                      |

|                               | For i = 0 to UpperBound, i++                                                                      |

|                               | IntRes1[j] OR= overridelfDataInvalid(BoolRes[j,i])                                                |

| Ranges                        | UpperBound = imm8[0] ? 7 : 15;                                                                    |

| (find characters from ranges) | IntRes1 = 0;                                                                                      |

|                               | For j = 0 to UpperBound, j++                                                                      |

|                               | For i = 0 to UpperBound, i+=2                                                                     |

|                               | IntRes1[j] OR= (overrideIfDataInvalid(BoolRes[j,i]) AND<br>overrideIfDataInvalid(BoolRes[j,i+1])) |

| Equal each                    | UpperBound = imm8[0] ? 7 : 15;                                                                    |

| (string compare)              | IntRes1 = 0;                                                                                      |

|                               | For i = 0 to UpperBound, i++                                                                      |

|                               | IntRes1[i] = overrideIfDataInvalid(BoolRes[i,i])                                                  |

| Equal ordered                 | UpperBound = imm8[0] ? 7 :15;                                                                     |

| (substring search)            | IntRes1 = imm8[0] ? 0xFF : 0xFFFF                                                                 |

|                               | For j = 0 to UpperBound, j++                                                                      |

|                               | For i = 0 to UpperBound-j, k=j to UpperBound, k++, i++                                            |

|                               | IntRes1[j] AND= overridelfDataInvalid(BoolRes[k,i])                                               |

#### Table 4-3. Aggregation Operation

# 4.1.4 Polarity

IntRes1 may then be further modified by performing a 1's complement, according to the value of the Imm8 Control Byte bit[4]. Optionally, a mask may be used such that only those IntRes1 bits which correspond to "valid" reg/mem input elements are complemented (note that the definition of a valid input element is dependant on the specific opcode and is defined in each opcode's description). The result of the possible negation is referred to as IntRes2.

#### Table 4-4. Polarity

| Imm8[5:4] | Operation             | Description                                                       |  |  |

|-----------|-----------------------|-------------------------------------------------------------------|--|--|

| 00b       | Positive Polarity (+) | IntRes2 = IntRes1                                                 |  |  |

| 01b       | Negative Polarity (-) | IntRes2 = -1 XOR IntRes1                                          |  |  |

| 10b       | Masked (+)            | IntRes2 = IntRes1                                                 |  |  |

| 11b       | Masked (-)            | IntRes2[i] = IntRes1[i] if reg/mem[i] invalid, else = ~IntRes1[i] |  |  |

# 4.1.5 **Output Selection**

#### Table 4-5. Ouput Selection

| Imm8[6]OperationObLeast significant index |                        | Description                                                               |

|-------------------------------------------|------------------------|---------------------------------------------------------------------------|

|                                           |                        | The index returned to ECX is of the least significant set bit in IntRes2. |

| 1b                                        | Most significant index | The index returned to ECX is of the most significant set bit in IntRes2.  |

For PCMPESTRI/PCMPISTRI, the Imm8 Control Byte bit[6] is used to determine if the index is of the least significant or most significant bit of IntRes2.

#### Table 4-6. Output Selection

| Imm8[6] Operation |                | Description                                                                                                                                                                                  |

|-------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ob                | Bit mask       | IntRes2 is returned as the mask to the least significant bits of XMM0 with zero extension to 128 bits.                                                                                       |

| 1b                | Byte/word mask | IntRes2 is expanded into a byte/word mask (based on imm8[1]) and placed in XMM0. The expansion is performed by replicating each bit into all of the bits of the byte/word of the same index. |

Specifically for PCMPESTRM/PCMPISTRM, the Imm8 Control Byte bit[6] is used to determine if the mask is a 16 (8) bit mask or a 128 bit byte/word mask.

# 4.1.6 Valid/Invalid Override of Comparisons

PCMPxSTRx instructions allow for the possibility that an end-of-string (EOS) situation may occur within the 128-bit packed data value (see the instruction descriptions below for details). Any data elements on either source that are determined to be past the EOS are considered to be invalid, and the treatment of invalid data within a comparison pair varies depending on the aggregation function being performed.

In general, the individual comparison result for each element pair BoolRes[i.j] can be forced true or false if one or more elements in the pair are invalid. See Table 4-7.

|                    |                         |                                | 2.72                        |                                 |                                    |  |  |

|--------------------|-------------------------|--------------------------------|-----------------------------|---------------------------------|------------------------------------|--|--|

| xmm1<br>byte/ word | xmm2/ m128<br>byte/word | lmm8[3:2] = 00b<br>(equal any) | Imm8[3:2] = 01b<br>(ranges) | lmm8[3:2] = 10b<br>(equal each) | lmm8[3:2] = 11b<br>(equal ordered) |  |  |

| Invalid            | Invalid                 | Force false                    | Force false                 | Force true                      | Force true                         |  |  |

| Invalid            | Valid                   | Force false                    | Force false                 | Force false                     | Force true                         |  |  |

| Valid              | Invalid                 | Force false                    | Force false                 | Force false                     | Force false                        |  |  |

| Valid              | Valid                   | Do not force                   | Do not force                | Do not force                    | Do not force                       |  |  |

### Table 4-7. Comparison Result for Each Element Pair BoolRes[i.j]

# 4.1.7 Summary of Im8 Control byte

#### Table 4-8. Summary of Imm8 Control Byte

| Imm8 | Description                                                                                                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0b   | 128-bit sources treated as 16 packed bytes.                                                                                                                      |

| 1b   | 128-bit sources treated as 8 packed words.                                                                                                                       |

| 0-b  | Packed bytes/words are unsigned.                                                                                                                                 |

| 1-b  | Packed bytes/words are signed.                                                                                                                                   |

| 00b  | Mode is equal any.                                                                                                                                               |

| 01b  | Mode is ranges.                                                                                                                                                  |

| 10b  | Mode is equal each.                                                                                                                                              |

| 11b  | Mode is equal ordered.                                                                                                                                           |

| b    | IntRes1 is unmodified.                                                                                                                                           |

| 1b   | IntRes1 is negated (1's complement).                                                                                                                             |

| 0b   | Negation of IntRes1 is for all 16 (8) bits.                                                                                                                      |

| 1b   | Negation of IntRes1 is masked by reg/mem validity.                                                                                                               |

| -0b  | Index of the least significant, set, bit is used (regardless of corresponding input element validity).<br>IntRes2 is returned in least significant bits of XMM0. |

| -1b  | Index of the most significant, set, bit is used (regardless of corresponding input element validity).<br>Each bit of IntRes2 is expanded to byte/word.           |

| 0b   | This bit currently has no defined effect, should be 0.                                                                                                           |

| 1b   | This bit currently has no defined effect, should be 0.                                                                                                           |

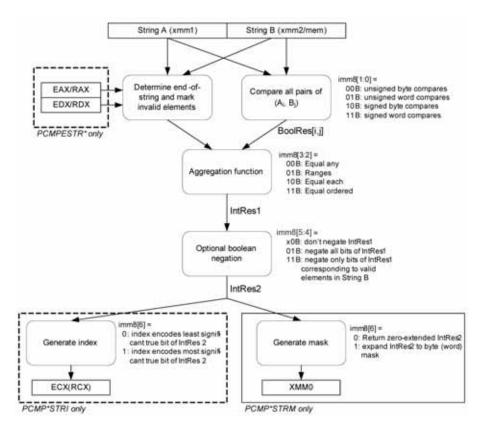

# 4.1.8 Diagram Comparison and Aggregation Process

Figure 4-1. Operation of PCMPSTRx and PCMPESTRx

# 4.2 INSTRUCTIONS (N-Z)

Chapter 4 continues an alphabetical discussion of Intel<sup>®</sup> 64 and IA-32 instructions (N-Z). See also: Chapter 3, "Instruction Set Reference, A-M," in the *Intel*® 64 and IA-32 Architectures Software Developer's Manual, Volume 2A.

# PCMPESTRI — Packed Compare Explicit Length Strings, Return Index

| Opcode/<br>Instruction                                           | Op/<br>En | 64/32 bit<br>Mode<br>Support | CPUID<br>Feature<br>Flag | Description                                                                                                           |

|------------------------------------------------------------------|-----------|------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 66 OF 3A 61 /r imm8<br>PCMPESTRI xmm1, xmm2/m128, imm8           | RMI       | V/V                          | SSE4_2                   | Perform a packed comparison of string data with explicit lengths, generating an index, and storing the result in ECX. |

| VEX.128.66.0F3A.WIG 61 /r ib<br>VPCMPESTRI xmm1, xmm2/m128, imm8 | RMI       | V/V                          | AVX                      | Perform a packed comparison of string data with explicit lengths, generating an index, and storing the result in ECX. |

#### Instruction Operand Encoding

| Op/En | Operand 1     | Operand 2     | Operand 3 | Operand 4 |

|-------|---------------|---------------|-----------|-----------|

| RMI   | ModRM:reg (r) | ModRM:r/m (r) | imm8      | NA        |

#### Description

The instruction compares and processes data from two string fragments based on the encoded value in the Imm8 Control Byte (see Section 4.1, "Imm8 Control Byte Operation for PCMPESTRI / PCMPESTRM / PCMPISTRI / PCMP-ISTRM"), and generates an index stored to the count register (ECX/RCX).

Each string fragment is represented by two values. The first value is an xmm (or possibly m128 for the second operand) which contains the data elements of the string (byte or word data). The second value is stored in an input length register. The input length register is EAX/RAX (for xmm1) or EDX/RDX (for xmm2/m128). The length represents the number of bytes/words which are valid for the respective xmm/m128 data.

The length of each input is interpreted as being the absolute-value of the value in the length register. The absolute-value computation saturates to 16 (for bytes) and 8 (for words), based on the value of imm8[bit3] when the value in the length register is greater than 16 (8) or less than -16 (-8).

The comparison and aggregation operations are performed according to the encoded value of Imm8 bit fields (see Section 4.1). The index of the first (or last, according to imm8[6]) set bit of IntRes2 (see Section 4.1.4) is returned in ECX. If no bits are set in IntRes2, ECX is set to 16 (8).

Note that the Arithmetic Flags are written in a non-standard manner in order to supply the most relevant information:

CFlag – Reset if IntRes2 is equal to zero, set otherwise ZFlag – Set if absolute-value of EDX is < 16 (8), reset otherwise SFlag – Set if absolute-value of EAX is < 16 (8), reset otherwise OFlag – IntRes2[0] AFlag – Reset PFlag – Reset

#### Effective Operand Size

| Operating mode/size | Operand 1 | Operand 2 | Length 1 | Length 2 | Result |

|---------------------|-----------|-----------|----------|----------|--------|

| 16 bit              | xmm       | xmm/m128  | EAX      | EDX      | ECX    |

| 32 bit              | xmm       | xmm/m128  | EAX      | EDX      | ECX    |

| 64 bit              | xmm       | xmm/m128  | EAX      | EDX      | ECX    |

| 64 bit + REX.W      | xmm       | xmm/m128  | RAX      | RDX      | RCX    |

#### Intel C/C++ Compiler Intrinsic Equivalent For Returning Index

int \_\_mm\_cmpestri (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

#### Intel C/C++ Compiler Intrinsics For Reading EFlag Results

- int \_mm\_cmpestra (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

- int \_mm\_cmpestrc (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

- int \_mm\_cmpestro (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

- int \_mm\_cmpestrs (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

- int \_\_mm\_cmpestrz (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

#### SIMD Floating-Point Exceptions

None.

#### **Other Exceptions**

See Exceptions Type 4; additionally, this instruction does not cause #GP if the memory operand is not aligned to 16 Byte boundary, and

#UD

# PCMPESTRM — Packed Compare Explicit Length Strings, Return Mask

| Opcode/<br>Instruction                                                  | Op/<br>En | 64/32 bit<br>Mode<br>Support | CPUID<br>Feature<br>Flag | Description                                                                                                                  |

|-------------------------------------------------------------------------|-----------|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 66 OF 3A 60 /r imm8<br>PCMPESTRM <i>xmm1, xmm2/m128, imm8</i>           | RMI       | V/V                          | SSE4_2                   | Perform a packed comparison of string data with explicit lengths, generating a mask, and storing the result in <i>XMMO</i>   |

| VEX.128.66.0F3A.WIG 60 /r ib<br>VPCMPESTRM <i>xmm1, xmm2/m128, imm8</i> | RMI       | V/V                          | AVX                      | Perform a packed comparison of string data with explicit lengths, generating a mask, and storing the result in <i>XMMO</i> . |

#### Instruction Operand Encoding

| Op/En | Operand 1     | Operand 2     | Operand 3 | Operand 4 |

|-------|---------------|---------------|-----------|-----------|

| RMI   | ModRM:reg (r) | ModRM:r/m (r) | imm8      | NA        |

#### Description

The instruction compares data from two string fragments based on the encoded value in the imm8 contol byte (see Section 4.1, "Imm8 Control Byte Operation for PCMPESTRI / PCMPESTRM / PCMPISTRI / PCMPISTRM"), and generates a mask stored to XMM0.

Each string fragment is represented by two values. The first value is an xmm (or possibly m128 for the second operand) which contains the data elements of the string (byte or word data). The second value is stored in an input length register. The input length register is EAX/RAX (for xmm1) or EDX/RDX (for xmm2/m128). The length represents the number of bytes/words which are valid for the respective xmm/m128 data.

The length of each input is interpreted as being the absolute-value of the value in the length register. The absolute-value computation saturates to 16 (for bytes) and 8 (for words), based on the value of imm8[bit3] when the value in the length register is greater than 16 (8) or less than -16 (-8).

The comparison and aggregation operations are performed according to the encoded value of Imm8 bit fields (see Section 4.1). As defined by imm8[6], IntRes2 is then either stored to the least significant bits of XMM0 (zero extended to 128 bits) or expanded into a byte/word-mask and then stored to XMM0.

Note that the Arithmetic Flags are written in a non-standard manner in order to supply the most relevant information:

CFlag – Reset if IntRes2 is equal to zero, set otherwise ZFlag – Set if absolute-value of EDX is < 16 (8), reset otherwise SFlag – Set if absolute-value of EAX is < 16 (8), reset otherwise OFlag –IntRes2[0] AFlag – Reset PFlag – Reset

Note: In VEX.128 encoded versions, bits (VLMAX-1:128) of XMM0 are zeroed. VEX.vvvv is reserved and must be 1111b, VEX.L must be 0, otherwise the instruction will #UD.

#### **Effective Operand Size**

| Operating mode/size | Operand1 | Operand 2 | Length1 | Length2 | Result |

|---------------------|----------|-----------|---------|---------|--------|

| 16 bit              | xmm      | xmm/m128  | EAX     | EDX     | XMM0   |

| 32 bit              | xmm      | xmm/m128  | EAX     | EDX     | XMM0   |

| 64 bit              | xmm      | xmm/m128  | EAX     | EDX     | XMM0   |

| 64 bit + REX.W      | xmm      | xmm/m128  | RAX     | RDX     | XMM0   |

#### Intel C/C++ Compiler Intrinsic Equivalent For Returning Mask

\_\_m128i \_mm\_cmpestrm (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

#### Intel C/C++ Compiler Intrinsics For Reading EFlag Results

- int \_\_mm\_cmpestra (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

- int \_\_mm\_cmpestrc (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

- int \_\_mm\_cmpestro (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

- int \_\_mm\_cmpestrs (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

- int \_\_mm\_cmpestrz (\_\_m128i a, int la, \_\_m128i b, int lb, const int mode);

#### SIMD Floating-Point Exceptions

None.

#### **Other Exceptions**

See Exceptions Type 4; additionally, this instruction does not cause #GP if the memory operand is not aligned to 16 Byte boundary, and

#UD

# PCMPISTRI — Packed Compare Implicit Length Strings, Return Index

| Opcode/<br>Instruction                                                  | Op/<br>En | 64/32 bit<br>Mode<br>Support | CPUID<br>Feature<br>Flag | Description                                                                                                           |

|-------------------------------------------------------------------------|-----------|------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 66 OF 3A 63 /r imm8<br>PCMPISTRI xmm1, xmm2/m128, imm8                  | RM        | V/V                          | SSE4_2                   | Perform a packed comparison of string data with implicit lengths, generating an index, and storing the result in ECX. |

| VEX.128.66.0F3A.WIG 63 /r ib<br>VPCMPISTRI <i>xmm1, xmm2/m128, imm8</i> | RM        | V/V                          | AVX                      | Perform a packed comparison of string data with implicit lengths, generating an index, and storing the result in ECX. |

#### Instruction Operand Encoding

| Op/En | Operand 1     | Operand 2     | Operand 3 | Operand 4 |

|-------|---------------|---------------|-----------|-----------|

| RM    | ModRM:reg (r) | ModRM:r/m (r) | imm8      | NA        |

#### Description

The instruction compares data from two strings based on the encoded value in the Imm8 Control Byte (see Section 4.1, "Imm8 Control Byte Operation for PCMPESTRI / PCMPESTRM / PCMPISTRI / PCMPISTRM"), and generates an index stored to ECX.

Each string is represented by a single value. The value is an xmm (or possibly m128 for the second operand) which contains the data elements of the string (byte or word data). Each input byte/word is augmented with a valid/invalid tag. A byte/word is considered valid only if it has a lower index than the least significant null byte/word. (The least significant null byte/word is also considered invalid.)

The comparison and aggregation operations are performed according to the encoded value of Imm8 bit fields (see Section 4.1). The index of the first (or last, according to imm8[6]) set bit of IntRes2 is returned in ECX. If no bits are set in IntRes2, ECX is set to 16 (8).

Note that the Arithmetic Flags are written in a non-standard manner in order to supply the most relevant information:

CFlag – Reset if IntRes2 is equal to zero, set otherwise

ZFlag - Set if any byte/word of xmm2/mem128 is null, reset otherwise

SFlag – Set if any byte/word of xmm1 is null, reset otherwise

OFlag -IntRes2[0]

AFlag – Reset

PFlag – Reset

Note: In VEX.128 encoded version, VEX.vvvv is reserved and must be 1111b, VEX.L must be 0, otherwise the instruction will #UD.

#### Effective Operand Size

| Operating mode/size | Operand1 | Operand 2 | Result |

|---------------------|----------|-----------|--------|

| 16 bit              | xmm      | xmm/m128  | ECX    |

| 32 bit              | xmm      | xmm/m128  | ECX    |

| 64 bit              | xmm      | xmm/m128  | ECX    |

| 64 bit + REX.W      | xmm      | xmm/m128  | RCX    |

#### Intel C/C++ Compiler Intrinsic Equivalent For Returning Index

int \_\_mm\_cmpistri (\_\_m128i a, \_\_m128i b, const int mode);

#### Intel C/C++ Compiler Intrinsics For Reading EFlag Results

- int \_mm\_cmpistra (\_\_m128i a, \_\_m128i b, const int mode);

- int \_\_mm\_cmpistrc (\_\_m128i a, \_\_m128i b, const int mode);

- int \_\_mm\_cmpistro (\_\_m128i a, \_\_m128i b, const int mode);

- int \_mm\_cmpistrs (\_\_m128i a, \_\_m128i b, const int mode);

- int \_\_mm\_cmpistrz (\_\_m128i a, \_\_m128i b, const int mode);

#### **SIMD Floating-Point Exceptions**

None.

#### **Other Exceptions**

See Exceptions Type 4; additionally, this instruction does not cause #GP if the memory operand is not aligned to 16 Byte boundary, and

#UD

# PCMPISTRM — Packed Compare Implicit Length Strings, Return Mask

| Opcode/<br>Instruction                                                  | Op/<br>En | 64/32 bit<br>Mode<br>Support | CPUID<br>Feature<br>Flag | Description                                                                                                                  |

|-------------------------------------------------------------------------|-----------|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 66 OF 3A 62 /r imm8<br>PCMPISTRM xmm1, xmm2/m128, imm8                  | RM        | V/V                          | SSE4_2                   | Perform a packed comparison of string data with implicit lengths, generating a mask, and storing the result in <i>XMMO</i> . |

| VEX.128.66.0F3A.WIG 62 /r ib<br>VPCMPISTRM <i>xmm1, xmm2/m128, imm8</i> | RM        | V/V                          | AVX                      | Perform a packed comparison of string data with implicit lengths, generating a Mask, and storing the result in <i>XMMO</i> . |

#### Instruction Operand Encoding

| Op/En | Operand 1     | Operand 2     | Operand 3 | Operand 4 |

|-------|---------------|---------------|-----------|-----------|

| RM    | ModRM:reg (r) | ModRM:r/m (r) | imm8      | NA        |

#### Description

The instruction compares data from two strings based on the encoded value in the imm8 byte (see Section 4.1, "Imm8 Control Byte Operation for PCMPESTRI / PCMPESTRM / PCMPISTRI / PCMPISTRM") generating a mask stored to XMM0.

Each string is represented by a single value. The value is an xmm (or possibly m128 for the second operand) which contains the data elements of the string (byte or word data). Each input byte/word is augmented with a valid/invalid tag. A byte/word is considered valid only if it has a lower index than the least significant null byte/word. (The least significant null byte/word is also considered invalid.)

The comparison and aggregation operation are performed according to the encoded value of Imm8 bit fields (see Section 4.1). As defined by imm8[6], IntRes2 is then either stored to the least significant bits of XMM0 (zero extended to 128 bits) or expanded into a byte/word-mask and then stored to XMM0.

Note that the Arithmetic Flags are written in a non-standard manner in order to supply the most relevant information:

CFlag - Reset if IntRes2 is equal to zero, set otherwise

ZFlag - Set if any byte/word of xmm2/mem128 is null, reset otherwise

SFlag – Set if any byte/word of xmm1 is null, reset otherwise

OFlag - IntRes2[0]

AFlag – Reset

PFlag – Reset

Note: In VEX.128 encoded versions, bits (VLMAX-1:128) of XMM0 are zeroed. VEX.vvvv is reserved and must be 1111b, VEX.L must be 0, otherwise the instruction will #UD.

#### Effective Operand Size

| Operating mode/size | Operand1 | Operand 2 | Result |

|---------------------|----------|-----------|--------|

| 16 bit              | xmm      | xmm/m128  | XMM0   |

| 32 bit              | xmm      | xmm/m128  | XMM0   |

| 64 bit              | xmm      | xmm/m128  | XMM0   |

| 64 bit + REX.W      | xmm      | xmm/m128  | XMM0   |

#### Intel C/C++ Compiler Intrinsic Equivalent For Returning Mask

\_\_m128i \_mm\_cmpistrm (\_\_m128i a, \_\_m128i b, const int mode);

#### Intel C/C++ Compiler Intrinsics For Reading EFlag Results

- int \_\_mm\_cmpistra (\_\_m128i a, \_\_m128i b, const int mode);

- int \_\_mm\_cmpistrc (\_\_m128i a, \_\_m128i b, const int mode);

- int \_\_mm\_cmpistro (\_\_m128i a, \_\_m128i b, const int mode);

- int \_\_mm\_cmpistrs (\_\_m128i a, \_\_m128i b, const int mode);

- int \_\_mm\_cmpistrz (\_\_m128i a, \_\_m128i b, const int mode);

#### SIMD Floating-Point Exceptions

None.

#### **Other Exceptions**

See Exceptions Type 4; additionally, this instruction does not cause #GP if the memory operand is not aligned to 16 Byte boundary, and

#UD